In the world of artificial intelligence and advanced computing, the transition from software to hardware implementation is a critical step in optimizing performance and efficiency. In this article, we delve into the intricate process of converting a large language model from English into an Application-Specific Integrated Circuit (ASIC). Join us as we explore the innovative methods and challenges involved in this groundbreaking endeavor.

Heading 1: Bridging the Gap: Translating Language Models into Hardware Designs

When it comes to translating cutting-edge language models into hardware designs, the journey from English text to an Application Specific Integrated Circuit (ASIC) implementation is both challenging and rewarding. With advancements in natural language processing (NLP) and deep learning, the need for efficient and scalable hardware implementations has never been more crucial. By bridging the gap between software models and hardware designs, we can unlock new possibilities for accelerated inference, real-time processing, and energy-efficient computing.

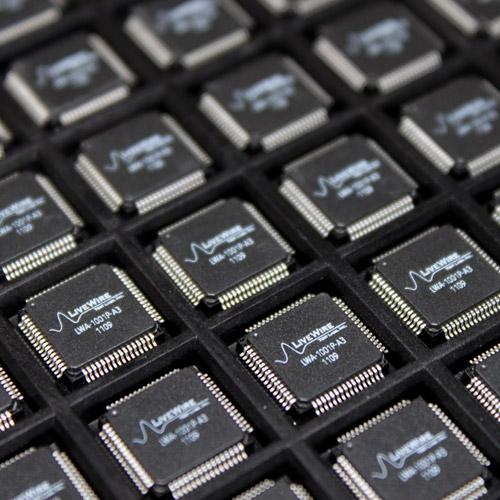

One approach to hardware implementation involves converting the large language model into a specialized ASIC chip that is optimized for specific NLP tasks. This process requires careful consideration of algorithmic optimizations, memory constraints, and parallel processing capabilities. By leveraging the strengths of custom hardware accelerators and flexible design methodologies, we can effectively transform complex language models into efficient and high-performance hardware solutions. Embracing the translation from English text to ASIC implementation opens up a world of opportunities for pushing the boundaries of language processing in the era of AI-driven technologies.

Heading 2: Challenges and Opportunities in Hardware Implementation of Large Language Models

When it comes to implementing large language models in hardware, there are both challenges and opportunities that need to be carefully considered. One of the main challenges is the sheer complexity of these models, which require significant computational power to run efficiently. This can pose a problem when trying to scale up the implementation to handle larger models or more complex tasks. Additionally, ensuring the hardware implementation is energy-efficient can be a hurdle, as large language models can be incredibly power-hungry.

On the flip side, there are also many exciting opportunities in hardware implementation of large language models. For example, creating custom ASICs tailored specifically for language processing tasks can lead to significant speedups and efficiency gains compared to running the models on general-purpose hardware. By optimizing the hardware architecture for the specific demands of language processing, we can unlock new possibilities for applications like natural language understanding and generation. Overall, tackling the challenges while embracing the opportunities in hardware implementation of large language models can open up a world of possibilities for more advanced and efficient AI systems.

Heading 3: Enhancing Efficiency with ASIC: Best Practices for Hardware Design

Exploring the realm of hardware design using ASIC can be a daunting task, especially when looking to enhance efficiency. One effective way to achieve this is by leveraging large language models in the process. By translating instructions from English into ASIC-friendly code, designers can streamline the implementation process and optimize their hardware design for peak performance.

Utilizing large language models not only simplifies the conversion of complex instructions into ASIC-compatible code but also ensures accuracy and consistency throughout the design process. With the ability to interpret and translate intricate details seamlessly, designers can save time and effort while maximizing the efficiency of their hardware design. By incorporating best practices for hardware design with ASIC, teams can unlock a new level of productivity and innovation in their projects.

Heading 4: Future Prospects and Innovations in Language Model Integration with ASIC Technology

When exploring the future prospects and innovations in language model integration with ASIC technology, one cannot overlook the groundbreaking advancements that have been made in implementing large language models on hardware. The synergy between language models and ASIC technology has paved the way for more efficient and powerful natural language processing applications.

With the increasing demand for faster and more accurate language processing capabilities, integrating language models with ASIC technology offers a promising solution. The ability to offload computationally intensive tasks to specialized hardware accelerators allows for quicker inference times and improved overall performance. This innovative approach not only enhances the efficiency of language models but also opens up new possibilities for a wide range of applications, from virtual assistants to machine translation systems. The future of language model integration with ASIC technology is indeed bright, promising unprecedented advancements in the field of natural language processing.

The Conclusion

As we come to the end of our exploration into the fascinating world of hardware implementation with large language models, it is clear that the intersection of English and ASIC technology holds endless possibilities for innovation and advancement. From enhancing natural language processing to revolutionizing AI capabilities, the journey from English to ASIC promises a future filled with exciting developments and breakthroughs. As we continue to push the boundaries of what is possible, one thing is certain – the fusion of language and technology will continue to shape the way we interact with the world around us. So let us embrace this journey with open minds and eager hearts, ready to unlock the full potential of this dynamic and ever-evolving field. The possibilities are endless, and the future is bright.